## SOFTWARE

## DEVELOPMENT

# НАМДВООК

Geoff Vincent

Jim Gill \_

Texas Instruments October 1981

#### IMPORTANT NOTICES

Texas Instruments reserves the right to make changes at any time to improve design and to supply the best possible product for the spectrum of users.

The Software Development Handbook is copyrighted by Texas Instruments, All rights reserved, No part of this publication may be reproduced in any manner including storage in a retrieval system or transmittal via electronic means, or other reproduction in any form or any method (electronic, mechanical, photocopying, recording or otherwise) without prior written permission of Texas **Instruments**.

Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patents or rights of others that may result from its use. No license is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

Copyright Texas Instruments 1981

<u>Note</u> "Texas Instruments" includes where the context permits Texas Instruments Incorporated, and any of its affiliated companies, including Texas Instruments Limited.

## PREFACE

This Second Edition of the Software Development Handbook has been extensively revised and updated to incorporate new developments, and to, improve and clarify the presentation.

As before, it is hoped that the book will appeal on several levels. The first three chapters are an introduction to the **technology, and assume little or no technical knowledge.** Chapter 1, which is introductory, describes the nature of software and the particular contribution of microsystems technology. Chapter 2 describes, step by step, the process of software development for microcomputers. Chapter 3 describes the tools of the software engineer. It is hoped that these chapters will appeal to those who have a peripheral interest in the technology, as well as to those who are or will become directly involved in software engineering.

Chapter 4 addresses the subject of **software design**, which we feel can and should be tackled separately from the discipline of programming in a particular language. The goal of appealing to a wide level of readership means that experienced software engineers will find some of the material familiar; however the approach may well be new, and some at least of the ideas will be novel. This chapter introduces suggested algorithmic and graphical notations for language independent software design. Those new to the technology are advised to read Chapter 4 in conjunction with some practical experience of programming in one of the languages **available**.

Chapter 5, Component Software, is the major new addition to the book. It describes a method of developing and packaging complex real time software functions. Such packages are available off the shelf from Texas Instruments for direct incorporation in application systems. Component Software is a significant step towards complete packaged functions, incorporating both hardware and software. These are likely to play an important part in microsystems technology in the future. Chapter 5 also includes a description of concurrency and the requirements of real time software.

Chapters 6, 7 and 8 describe in turn Microprocessor Pascal, Power BASIC, and 9900/99000 Assembly Language. These chapters are not intended to be complete language tutorials. Tutorials are available elsewhere; and it is felt that programming is best taught by a combination of

personal tuition and practical experience. Courses on programming are available from various sources, including Texas Instruments. Rather, these chapters are designed to give a feel for each language, its important features, and its areas of application. Microprocessor Pascal is a professional programmer's tool which permits the construction of reliable, real time software systems of any level of **complexity.** Power BASIC is a much simpler language that can be learned in a few hours, and can be used even by non software professionals to provide quick solutions to simple problems. Assembly language provides direct access to all the resources of the microcomputer, and can be used in critical areas of a system to "fine tune" for maximum performance. Naturally, effective use of assembly language requires a certain level of skill. Chapter 8 contains an extensive "Algorithms and Techniques" section, describing some commonly used solutions to specific problems. Each chapter includes, besides the language description, а Reference Section that tabulates the vital elements of each language.

This handbook is not intended as a complete course in software development for microcomputers. However, with appropriate additional material and combined with practical experience of one or more of the languages described, it could form the basis for such a course. The aim is to provide a Handbook for the emerging discipline of software engineering for microcomputers, and to begin the process of identifying and communicating those elements of the technology that will prove to be of lasting value. This book is a distillation of the practical experience of software engineers, and **it** is hoped that it will make some , contribution to those entering on or already immersed in the technology.

The authors wish to thank all those who have contributed approaches, ideas, descriptions or actual software examples, and without whom this book could not have been written,

Geoff Vincent Jim Gill

October 1981

| We would  | appreciate | your | comm | lents | on | the   | useful | ness | of   | this  |

|-----------|------------|------|------|-------|----|-------|--------|------|------|-------|

| handbook  | . Please   | comp | lete | and   | re | eturr | n this | form | n to | ) the |

| address ( | overleaf∎  |      |      |       |    |       |        |      |      |       |

|    | Name: (last)                   | (firs                                                                               | t):              |

|----|--------------------------------|-------------------------------------------------------------------------------------|------------------|

|    | Company:                       | Posit                                                                               | ion:             |

|    | Address:                       |                                                                                     |                  |

|    |                                |                                                                                     |                  |

|    |                                | Country:                                                                            | •                |

|    |                                |                                                                                     |                  |

| 1. |                                | ook well organised? Yes                                                             | No               |

|    |                                | ······································                                              |                  |

| 2. |                                | correctly presented and<br>Yes No                                                   | adequately       |

|    |                                |                                                                                     |                  |

| 3. | What subject                   | matter could be expand                                                              | ed or clarified? |

|    |                                |                                                                                     | ·····            |

| 4. | -                              | tly involved in softwa<br>te your main <b>area(s)</b> c                             | -                |

|    |                                |                                                                                     |                  |

|    | (a) As an int<br>(b) As a sour | d this handbook useful<br>croduction to the field<br>cce of <b>ideas/informatio</b> | n                |

|    | (d) In any of                  | erence book<br>.her way(please specif                                               | <u>v</u> )       |

|    |                                | mer way (prease specif                                                              | <i></i>          |

| 6. |                                | y Texas Instruments so<br>ation on these product                                    |                  |

|    |                                |                                                                                     |                  |

| 7. | Any other com                  | ments                                                                               |                  |

Please mail this sheet to:

M/S 35 Microprocessor Group TEXAS INSTRUMENTS Ltd Manton Lane Bedford MK41 7PA ENGLAND

# TABLE OF CONTENTS

Section

Title

Page

# CHAPTER **1** INTRODUCTION

| 1.1   | WHAT IS SOFTWARE .   | •    | •   | •   | •   | •    | • | • | • | • | • | 1-1  |

|-------|----------------------|------|-----|-----|-----|------|---|---|---|---|---|------|

| 1.2   | BLACK BOXES AND DIGI | TAL  | EL  | ЕСТ | RON | VICS |   | - | - |   | • | 1-5  |

| 1.3   | COMPUTERS            | •    | •   | •   | •   | •    | • | • | • | • | • | 1-7  |

| 1.4   | SOFTWARE DEVELOPMENT | [    | •   | •   | •   | •    | • | • | • | • | • | 1-12 |

| 1.5   | GENERAL PURPOSE COMI | PUTE | RS  | •   | •   | •    | • | • | • | • | • | 1-14 |

| 1.6   | DEDICATED COMPUTERS  | •    | •   | •   | •   | •    | • | • | • | • | • | 1-16 |

| 1.7   | ROM AND RAM - SEMICO | NDU  | TOR | ME  | MOR | Y    | - | - | - |   | - | 1-17 |

| 1.7.1 | ROM Types 🔹 🔹        |      |     | -   |     |      |   |   | - |   | - | 1-17 |

| 1.7.2 | RAM Types 🔹 🔹        |      | -   | -   | -   | -    | - |   | - |   | - | 1-18 |

| 1.7.3 | ROM/RAM Summary      | -    |     | -   | •   |      | - |   | - | - | - | 1-19 |

| 1.8   | APPLICATIONS         | •    | •   | •   | •   | •    | • | • | • | • | • | 1-20 |

| 1.9   | FUTURE DEVELOPMENTS  |      | •   | •   | -   | -    | - |   | - |   | • | 1-22 |

|       |                      |      |     |     |     |      |   |   |   |   |   |      |

## CHAPTER 2 SOFTWARE DEVELOPMENT

| 2.1    | THE SOFTW. | ARE D  | DEVEL | LOPN | 1ENT | PRO | CES | S   | • | ٠ | • | • | • | 2-1               |

|--------|------------|--------|-------|------|------|-----|-----|-----|---|---|---|---|---|-------------------|

| 2.2    | FUNCTIONA  | L SPE  | CIFI  | САТ  | ION  | •   | •   | •   | • | • | • | • | • | 2-3               |

| 2.3    | SYSTEM DE  | SIGN   |       |      | •    | •   |     | -   | - |   |   |   |   | 2-5               |

| 2.3.1  | Documen    | ntatio | n 🛛   |      |      |     |     | -   |   |   |   |   | - | 2-7               |

| 2.4    | HARDWARE   | DESIG  | N .   |      | •    | •   | •   | •   | ٠ | • | • | • | • | 2-8               |

| 2.4.1  | Estimat    | ing S  | yste  | m L  | oad  |     |     | -   |   |   |   |   |   | 2-9               |

| 2.4.2  | Memory     | Size   | •     |      |      |     | -   | -   |   |   |   |   |   | 2-11              |

| 2.5    | SOFTWAREI  | DESIG  | N.    |      | •    | •   | •   | •   | • | • | • | • | • | 2-11              |

| 2.6    | PROGRAMMI  | NG     | • •   |      | •    | •   | •   | •   | • | • | • | • | • | 2-13              |

| 2.7    | PROGRAM T  | RANSL  | ATIC  | N.   | •    | •   | •   | •   | • | • | • | • | • | 2-14              |

| 2.8    | CONFIGURA  | TION   | AND   | LIN  | KINC | •   | •   | •   | • | • | • | • | • | 2-15              |

| 2.9    | DEBUGGING  | •      | • •   |      | •    | •   | •   | •   | • | • | • | • | • | 2-15              |

| 2.9.1  | Simulat    | ion    |       |      |      |     | -   | -   |   |   |   |   |   | 2-15              |

| 2.10   | HARDWARE   | INTEG  | RATI  | ON   | AND  | EVA | LUA | TIO | Ν | • | • | • | • | 2-16              |

| 2.10.1 | Emulati    | o n    |       |      |      |     |     | -   |   |   |   |   |   | 2-16              |

| 2.10.2 | Evaluat    | ion    |       |      |      |     | -   |     |   |   |   |   |   | 2-17              |

| 2.11   | PRODUCTION | • /    | • •   |      | •    | •   | •   | •   | • | • | • | • | • | 2 <del>-</del> 18 |

# CHAPTER **3** DEVELOPMENT TOOLS

| 3.1 | OVERVIEW | V           | • | •    | •   | • | • | • | • | • | • | • | • | • | • | 3-1 |

|-----|----------|-------------|---|------|-----|---|---|---|---|---|---|---|---|---|---|-----|

| 3.2 | DEVELOPM | <b>MENT</b> | S | YSTE | EMS | • | • | • | • | • | • | • | • | • | • | 3-1 |

| 3.3 | FILES    | •           | • | •    | •   | • | • | • | • | - |   | • | • | • | • | 3-2 |

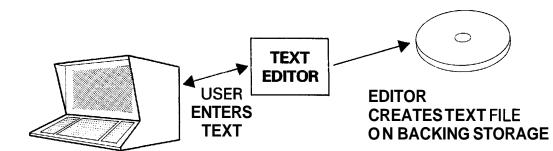

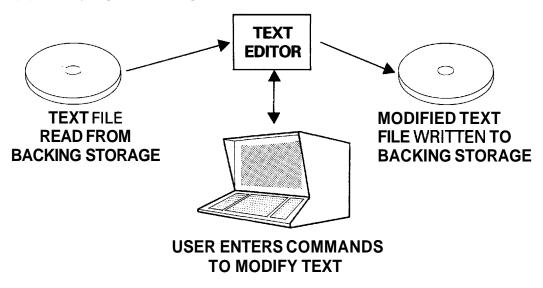

| 3.3.1   | B a c k u p s  |       |         |         |      |      |       |   |   |   |   |   |   | 3-3  |

|---------|----------------|-------|---------|---------|------|------|-------|---|---|---|---|---|---|------|

| 3.4     | <b>_</b>       | •     | •       |         |      | •    | •     | • | • | • | • | • | • | 3-5  |

| 3.5     | PROGRAMMING LA | NGU   | JAGI    | ES      | •    | •    | •     | • | • | • | • | • | • | 3-8  |

| 3.5.1   | Assembly Lan   | g u a | a g e   |         |      |      |       |   |   |   |   |   |   | 3-8  |

| 3.5.2   | Assemblers     |       |         |         |      | -    | -     |   | - |   |   | - |   | 3-9  |

| 3.5.3   | High- Level L  | ang   | guag    | ges     | •    | •    | •     | • | • | • | • | • | • | 3-10 |

| 3.5.4   | Pascal.        | •     | •       | •       | •    | •    | •     | • | • | • | • | • | • | 3-12 |

| 3.5.5   | Compilers      |       |         |         | -    |      |       |   |   |   |   |   |   | 3-13 |

| 3.5.6   | Interpreted    | Lar   | n g u a | n g e s | 5    | •    | ٠     | • | • | • | • | • | • | 3-13 |

| 3.5.6.1 | BASIC .        | •     | •       | •       | •    | •    | •     | • | • | • | • | ٠ | • | 3-14 |

| 3.5.6.2 | Interprete     |       |         |         |      |      |       |   |   |   |   | • | • | 3-14 |

| 3.5.7   | High- Level v  | s L   | _ o w - | – Le    | vel  | •    | •     | • | • | • | • | • | • | 3-15 |

| 3.6     | LINKER • •     | •     | •       | •       | •    | ٠    | •     | • | • | • | • | • | • | 3-16 |

| 3.6.1   | Absolute and   | R     | eloc    | cata    | ıble | e Co | o d e | • | • | • | • | • | • | 3-16 |

| 3.7     | TARGET SYSTEM  | EXI   | ECUI    | LION    | I    | •    | •     | • | • | • | • | • | • | 3-18 |

| 3.7.1   | Loader         |       |         |         |      |      |       |   |   |   |   |   |   | 3-18 |

| 3.7.2   | PROM Program   | m e   | r       |         |      |      |       |   |   |   |   |   |   | 3-19 |

| 3.8     | TEXT FILES     | •     | ٠       | •       | •    | •    | •     | • | • | • | • | • | • | 3-19 |

# CHAPTER 4 SOFTWARE DESIGN

| 4.1          | OVERVIEW • • • • • • • • • • • •     | 4-1          |

|--------------|--------------------------------------|--------------|

| 4.2          | SOFTWARE STRUCTURE                   | 4-2          |

| 4.3          | SOFTWARE PACKAGES                    | 4-3          |

| 4.4          | DESIGNLANGUAGE • • • • • • • • • •   | 4-4          |

| 4.5          | ALGORITHMS • • • • • • • • • • •     | 4-5          |

| 4.5.1        | Sequence                             | 4-7          |

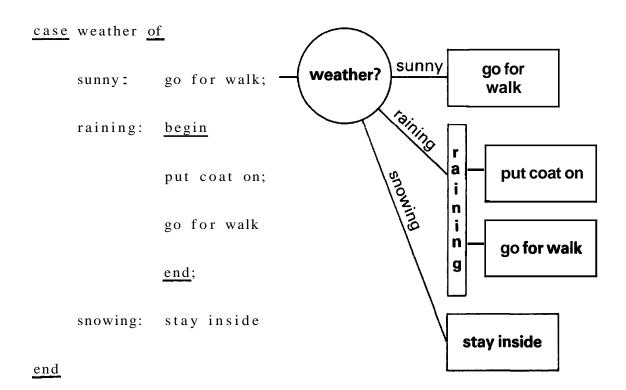

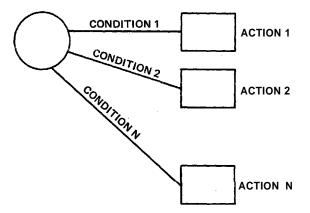

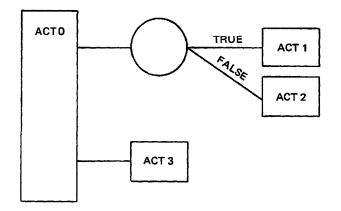

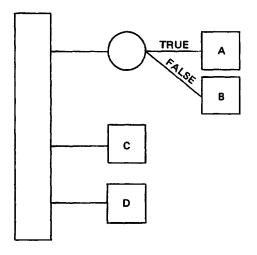

| 4.5.2        | Selection                            | 4-9          |

| 4.5.3        | Algorithm Design                     | 4-12         |

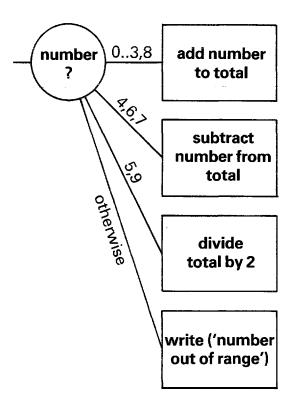

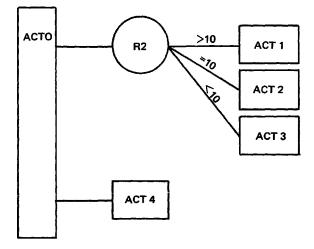

| 4.5.4        | The CASE Construct                   | 4-14         |

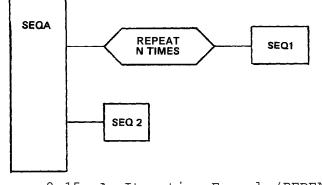

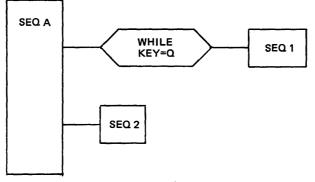

| 4.5.5        | Iteration                            | 4-16         |

| 4.5.6        | Structured Programming               | 4-18         |

| 4.6          |                                      | 4-19         |

| 4.6.1        | Data Types                           | 4-20         |

| 4.6.2        | Variables                            | 4-22         |

| 4.6.3        |                                      | 4-23         |

| 4.0.5        |                                      | 4-26         |

|              |                                      | 4-20         |

| 4.7<br>4.7.1 |                                      | 4-20         |

|              | Records                              | 4-27         |

| 4.7.2        | Arrays                               | 4-28<br>4-31 |

| 4.7.3        | Dynamic Data Structures              |              |

| 4.7.4        | Data Diagrams                        | 4-32<br>4-34 |

| 4.8          | DESIGN APPROACHES                    |              |

| 4.9          | BLOCK STRUCUTRE • • • • • • • • •    | 4-38         |

| 4.10         | PROCEDURES AND FUNCTIONS • • • • • • | 4-39         |

| 4.10.1       | Parameter Passing                    | 4-43         |

| 4.11         | REAL TIME SOFTWARE • • • • • • • •   | 4-44         |

| 4.11.1       | Semaphores                           | 4-46         |

| 4.11.2       | Executives                           | 4-47         |

| 4.11.3       | interrupts                           | 4-47         |

| 4.12         | MAKING TEA • • • • • • • • • • •     | 4-49         |

| 4.13         | BIBLIOGRAPHY • • • • • • • • • •     | 4-54         |

|              |                                      |              |

## CHAPTER 5 COMPONENT SOFTWARE

| 5.1<br>5.1.1 | WHAT IS COMPONENT SOFTWARE                   | 5-1<br>5-3        |

|--------------|----------------------------------------------|-------------------|

| 5.1.2        | Function to Function Architecture            | 5-6               |

| 5.2          | THE COMPONENT SOFTWARE ENVIRONMENT • • • • • | 5-7               |

| 5.2.1        | Concurrency                                  | 5-7               |

| 5.2.1.1      | Packaged Functions                           | 5-9               |

| 5.2.1.2      | Implementation of Concurrency                | 5 <del>-</del> 10 |

| 5.2.1.3      | Levels of Concurrency                        | 5 <b>-</b> 11     |

| 5.2.2        | Data and Re-entrancy                         | 5-12              |

| 5.2.2.1      | Memory Allocation                            | 5-14              |

| 5.2.2.2      | Multiple Activations                         | 5-15              |

| 5.2.3        | The Realtime Executive                       | 5 <del>-</del> 15 |

| 5.2.3.1      | Channels and Interprocess Files              | 5-16              |

| 5.2.3.2      |                                              | 5-17              |

| 5.2.4        | File I/O Standards                           | 5-19              |

| 5.2.4.1      | 1/0 Subsystems                               | 5-19              |

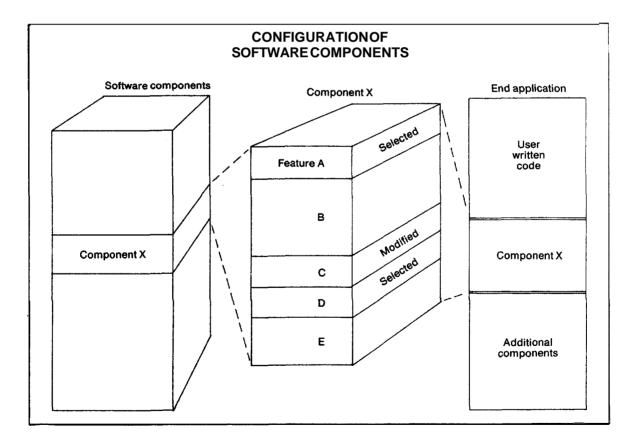

| 5.2.5        | Configuration                                | 5-21              |

| 5.2.6        | Customisation                                | 5-23              |

| 5.2.7        | Microprocessor Pascal                        | 5-22              |

| 5.2.7.1      | Code Efficiency                              | 5-24              |

| 5.2.7.2      |                                              | 5-24              |

| 5.2.7.3      | Microprocessor Pascal and Component Software | 5-26              |

| 5.2.8        | Other Languages                              | 5-26              |

| 5.2.9        | Hardware                                     | 5-26              |

| 5.2.10       | Component Software Products • • • • • •      | 5-28              |

| 5.2.11       | Silicon Functions                            | 5-28              |

| 5.3          | BIBLIOGRAPHY                                 | 5-30              |

## CHAPTER 6 MICROPROCESSOR PASCAL

| 6.1   | INTRODUCTION                                       | 6-1  |

|-------|----------------------------------------------------|------|

| 6.2   | TEXAS INSTRUMENTS IMPLEMENTATIONS • • • • •        | 6-3  |

| 6.3   | MICROPROCESSOR PASCAL OVERVIEW • • • • • •         | б-4  |

| 6.3.1 | Features • • • • • • • • • • • •                   | 6-4  |

| 6.3.2 | Stack and Heap · · · · · · · · · · · ·             | 6-5  |

| 6.3.3 | Systems and Programs                               | 6-6  |

| 6.3.4 | Processes and Procedures                           | 6-6  |

| 6.3.5 | Declarations and Statements • • • • • •            | 6-6  |

| 6.3.6 | Block Structure • • • • • • • • • •                | б-8  |

| 6.4   | MICROPROCESSOR PASCAL SYSTEM _ PROGRAMMING SUPPORT |      |

|       | ENVIRONMENT • • • • • • • • • • •                  | 6-11 |

| 6.4.1 | Microprocessor Pascal Editor 🛛 🔹 🔹 🔹 🔹             | 6-12 |

| 6.4.2 | Microprocessor Pascal Compiler and Code Generator  | 6-14 |

| 6.4.3 | Microprocessor Pascal Host Debugger , , ,          | 6-16 |

| 6.5   | MICROPROCESSOR PASCAL LANGUAGE • • • • • •         | 6-17 |

| 6.5.1 | Basic Language Elements                            | 6-17 |

| 6.5.2 | Character Set • • • • • • • • • •                  | 6-17 |

| 6.5.3 | Keywords • • • • • • • • • • • •                   | 6-17 |

| 6.5.4   | Identifiers                                     | 6-18              |

|---------|-------------------------------------------------|-------------------|

| 6.5.5   | Language Element Separators 🛛 🖬 🖬 🔹 🖬           | 6-19              |

| 6.5.6   | Comments                                        | 6-19              |

| 6.5.7   | Constants                                       | 6-19              |

| 6.5.8   | Variables                                       | 6-20              |

| 6.5.9   | Expressions                                     | 6-21              |

| 6.5.9.1 | Operands                                        | 6-21              |

| 6.5.9.2 | Operators                                       | 6-21              |

| 6.5.9.3 | Function Calls                                  | 6-22              |

| 6.5.10  | Assignment Statement , , , , , , , , ,          | 6-23              |

| 6.5.11  | Routine Declaration                             | 6-23              |

| 6.6     | DATATYPES                                       | 6-25              |

| 6.6.1   | User Defined Types                              | 6-26              |

| 6.6.2   | Integer and Longint Type 🔹 🔹 🔹 🔹 🔹 🔹            | 6-27              |

| 6.6.3   | Boolean Type                                    | 6-27              |

| 6.6.4   | Char Type – – – – – – – – – – – – – – – – – – – | 6 <del>-</del> 27 |

| 6.6.5   | Enumeration Type                                | 6-28              |

| 6.6.6   | Subrange Type                                   | 6-29              |

| 6.6.7   | Real Type                                       | 6-29              |

| 6.6.8   | Semaphore Type                                  | 6-30              |

| 6.6.9   | Array Type                                      | 6-30              |

| 6.6.10  | Record Type                                     | 6-31              |

| 6.6.11  | Set Type                                        | 6-33              |

| 6.6.12  | File Type в в в в в в в в в в                   | 6-33              |

| 6.6.13  | Pointer Type                                    | 6-34              |

| 6.6.14  | Type Compatibility                              | 6-36              |

| 6.7     | CONTROL STRUCTURES                              | 6-37              |

| 6.7.1   | Procedure Statement , , , , , , , , ,           | 6-37              |

| 6.7.2   | Compound Statement                              | 6-38              |

| 6.7.3   | IF Statement                                    | 6-39              |

| 6.7.4   | CASE Statement                                  | 6-39              |

| 6.7.5   | FOR Statement                                   | 6-41              |

| 6.7.6   | WHILE Statement                                 | 6-42              |

| 6.7.7   | ESCAPE Statement                                | 6-44              |

| 6.7.8   | GOTO Statement                                  | 6-45              |

| 6.8     | CONCURRENCY                                     | 6-46              |

| 6.8.1   | Processes • • • • • • • • • • •                 | 6-46              |

| 6.8.2   | Process Record                                  | 6-47              |

| 6.8.3   | Process Scheduling                              | 6-47              |

| 6.8.4   | Process Synchronization                         | 6-48              |

| 6.8.4.1 | Semaphores                                      | 6-48              |

| 6.8.4.2 | Wait Operation                                  | 6-49              |

| 6.8.4.3 | Signal Operation                                | 6-49              |

| 6.8.5   | Interprocess Communication                      | 6-51              |

| 6.8.5.1 | Shared Variables                                | 6-51              |

| 6.8.5.2 | Message Buffers                                 | 6-51              |

| 6.8.5.3 | Channels                                        | 6-53              |

| 6.8.5.4 | Interprocess Files • • • • • • • •              | 6-55              |

| 6.9     | MODULARITY • • • • • • • • • • • •              | 6-57              |

| 6.10    | INTERRUPTS • • • • • • • • • • •                | 6-60              |

| 6.11    | INPUT/OUTPUT                                    | 6-62              |

| 6.11.1  | CRU Operations                                  | 6-62              |

| 6.11.2  | Memory-Mapped I/O                               | 6-62              |

| 6.11.3  | Files                                           | 6-64              |

| 6.12    | DIGITAL VOLTMETER (DVM) EXAMPLE • • • • •       | 6-65              |

|         |                                                 |                   |

...

| 6.13 REFE        | ERENCE SECTION  | • •     | • •    | • •             | •            | • •   | • | 6-72              |

|------------------|-----------------|---------|--------|-----------------|--------------|-------|---|-------------------|

| <b>6.13.1</b> Sy | stem Commands   |         |        |                 | -            |       | - | 6-72              |

| <b>6.13.2</b> Ut | ility Commands  | (990/4  | and 1  | гмам <b>9</b> 0 | <b>00</b> on | ly)   | - | 6-72              |

| <b>6.13.3</b> Ed | dit Commands 🔹  |         |        |                 | -            |       | - | 6-73              |

| 6.13.4 De        | ebug Commands . |         |        |                 |              |       |   | 6-74              |

| 6.13.5 Fi        | lle Manipulatio | n Routi | nes 🛯  |                 | -            |       | - | 6-76              |

|                  | rithmetic Routi |         |        |                 |              |       |   | 6 <del>-</del> 78 |

| 6.13.7 CR        | RU Routines 🔹   |         |        |                 | -            |       | - | 6-79              |

| <b>6.13.8</b> Mi | iscellaneous Ro | utines  |        |                 | •            |       |   | 6-80              |

| 6.13.9 Rx        | k Routines 🖬 🖬  |         |        |                 | •            |       |   | 6-80              |

| 6.13.9.1         | Processor Mana  | gement  | (Sched | iuling          | ) Rou        | tines | - | 6-80              |

| 6.13.9.2         | Semaphore Rout  |         |        | -               | -            |       | - | 6-80              |

| 6.13.9.3         | Semaphore Attr  | ibute R | outine | es .            | •            |       | • | 6-81              |

| 6.13.9.4         | Interrupt Rout  | ines 🛯  |        |                 | -            |       | - | 6-82              |

| 6.13.9.5         | Process Manage  | ment Ro | utines | 5               | •            | • •   | • | 6-82              |

| 6.13.9.6         | Heap Managemen  | t Routi | nes .  | • •             | •            | • •   | • | 6-83              |

| 6.13.9.7         | Channel 1/0 Ro  |         |        |                 |              |       | • | 6-83              |

| 6.13.9.8         | Interprocess F  | ile Tra | nsfer  | Routi           | nes          | • •   | • | 6-84              |

| 6.13. <b>9.9</b> | Exception Hand  | ling Ro | utines | s.,             | •            |       | • | 6-85              |

| 6.13.9.10        | Critical Trans  | action  | Routir | nes .           | •            | • •   | • | 6-86              |

| 6.13.9.11        | Rx Error and E  | xceptio | n Code | es .            | •            | • •   | • | 6-86              |

| 6.13.10 Ba       | ackus-Naur Form | (BNF)   | Syntax | k Deffi         | nitio        | ns 🛯  | - | 6-89              |

| 6.13.10.1        | Compiler Optio  | ns .    | • •    | • •             | •            | • •   | • | 6-89              |

| 6.13.10.2        | Concurrent Cha  | racteri |        |                 |              | • •   | • | 6-90              |

| 6.13.10.3        | System Declara  | tion 🛯  |        |                 | -            |       | - | 6-90              |

| 6.13.10.4        | Type Syntax 🔹   |         |        |                 |              |       | - | 6-92              |

| 6.13.10.5        | Statement Synt  |         |        |                 |              |       | - | 6-94              |

| 6.13.10.6        | Expression Syn  | tax 🔳   |        |                 |              |       | - | 6-95              |

| 6.13.10.7        | Variable Synta  | X       |        |                 | -            |       | • | 6-96              |

| 6.13.10.8        | Constant Expre  | ssion S | yntax  | • •             | •            | • •   | • | 6-97              |

|                  | Language Eleme  | nt Synt | ax 🛛   |                 | -            |       | • | 6-97              |

| 6.14 BIBI        | LIOGRAPHY       | •••     | • •    | • •             | •            | • •   | • | 6-99              |

# CHAPTER **7** POWER BASIC

| 7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.3 | POWERBASIC       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | -1<br>-2<br>-3<br>-4<br>-5<br>-8 |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 7.4                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -10                              |

| 7.4.1                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -10                              |

| 7.4.2                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -10                              |

| 7.4.3                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -11                              |

| 7.4.4                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -12                              |

| 7.5                                          | VARIABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -12                              |

| 7.5.1                                        | Variable Names 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -13                              |

| 7.5.2                                        | Variable Declaration 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -13                              |

| 7.5.3                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -14                              |

| 7.5.3.1                                      | Integer Variables • • • • • • • • • 7·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -14                              |

| 7.5.3.2                                      | Floating Point Variables 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -14                              |

| 7.5.3.3                                      | Character String Variables • • • • • • • 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -14                              |

| 7.5.3.4  | Array Variables • • • • • • • • • •        | 7 <b>-</b> 15     |

|----------|--------------------------------------------|-------------------|

| 7.6      | POWER BASIC PROGRAM • • • • • • • • •      | 7 <del>-</del> 15 |

| 7.6.1    | Control Statements • • • • • • • • •       | 7-16              |

| 7.6.1.1  | <b>GOTO</b> 'Statement                     | <b>7-</b> 16      |

| 7.6.1.2  | IF THEN Statement                          | 7-16              |

| 7.6.1.3  | ELSE Statement • • • • • • • • •           | 7-19              |

| 7.6.1.4  | FOR NEXT Statement                         | 7-20              |

| 7.6.2    |                                            | 7-23              |

| 7.6.3    |                                            | 7-26              |

| 7.6.4    |                                            | 7-27              |

| 7.6.5    |                                            | 7-28              |

|          | CRU Operations                             | 7-28              |

| 7.6.5.1  | BASE Statement • • • • • • • • • •         |                   |

| 7.6.5.2  | CRB Function • • • • • • • • • •           | 7-28              |

| 7.6.5.3  | CRF Function                               | 7-29              |

| 7.6.6    | Memory Operations • • • • • • • • •        | 7-29              |

| 7.6.6.1  | MEM Function                               | 7-29              |

| 7.6.6.2  | MWD Function                               | 7-30              |

| 7.6.7    | Assembly Language Routines 🕡 👝 👝 👝 🖡       | 7-31              |

| 7.6.8    | Interrupts                                 | 7-32              |

| 7.6.8.1  | IMASK Statement                            | 7 <b>-</b> 34     |

| 7.6.8.2  | TRAP Statement • • • • • • • • • •         | 7-34              |

| 7.6.8.3  | IRTN Statement • • • • • • • • • •         | 7 <del>-</del> 35 |

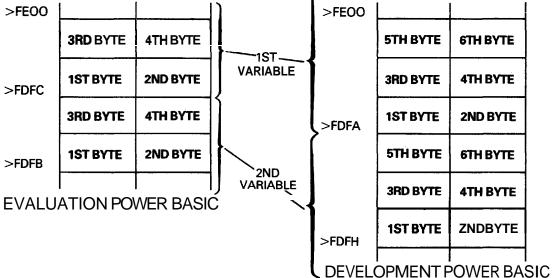

| 7.7      | POWER BASIC STORAGE ALLOCATION • • • • • • | 7-35              |

| 7.7.1    | Variable Storage • • • • • • • • • •       | 7-35              |

| 7.7.1.1  | Integer Format • • • • • • • • •           | 7-36              |

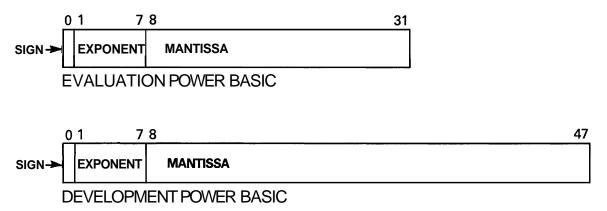

| 7.7.1.2  | Floating Point Format                      | 7-37              |

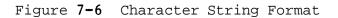

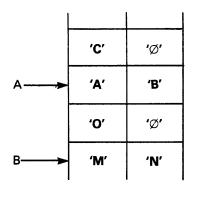

| 7.7.1.3  | Character String Format                    | 7-37              |

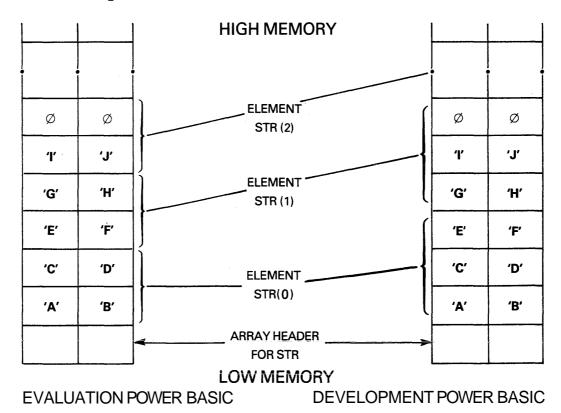

| 7.7.1.4  | Array Storage • • • • • • • • • •          | 7-38              |

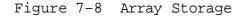

| 7.7.2    | System Memory Map                          | 7 <del>-</del> 40 |

| 7.8      | REFERENCE SECTION                          | 7-43              |

| 7.8.1    | Character Set                              | 7-43              |

| 7.8.2    |                                            | 7-43              |

| 7.8.3    |                                            | 7-43              |

|          |                                            |                   |

| 7.8.4    | Edit Commands • • • • • • • • • •          | 7-43              |

| 7.8.5    | Power BASIC Commands                       | 7-44              |

| 7.8.6    | Power BASIC Statements                     | 7-45              |

| 7.8.7    | Operators                                  | 7-49              |

| 7.8.7.1  | Arithmetic Operators                       | 7-49              |

| 7.8.7.2  | Relational Operators • • • • • • • •       | 7-49              |

| 7.8.7.3  | Boolean Operators • • • • • • • • •        | 7-49              |

| 7.8.7.4  | Logical Operators • • • • • • • •          | 7-49              |

| 7.8.7.5  | Operator Precedence 🔹 🔹 🔹 🔹 🔹 🔹            | 7 <del>-</del> 50 |

| 7.8.8    | Arithmetic Functions                       | 7-50              |

| 7.8.9    | CRU Operations                             | 7-51              |

| 7.8.9.1  | CRB Function                               | 7 <del>-</del> 51 |

| 7.8.9.2  | CRF Function                               | 7 <del>-</del> 51 |

| 7.8.10   | Memory Functions                           | 7 <del>-</del> 52 |

| 7.8.10.3 |                                            | 7 <del>-</del> 52 |

| 7.8.10.2 | MEM Function                               | 7 <del>-</del> 52 |

| 7.8.10.3 | MWD Function                               | 7-52              |

| 7.8.11   | Miscellaneous Functions                    | 7-53              |

| 7.8.11.1 |                                            | 7-53              |

| 7.8.11.2 |                                            | 7 <del>-</del> 53 |

| 7.8.11.3 |                                            | 7 <del>-</del> 53 |

| 7.8.12   | String Operations • • • • • • • • • •      | 7 <b>-</b> 54     |

| / •••••  |                                            |                   |

| 7.8.13 | String Functions • • • • • • • • • • | 7-55              |

|--------|--------------------------------------|-------------------|

| 7.8.14 | INPUT Options                        | 7-56              |

| 7.8.15 | PRINT Options                        | 7 <del>-</del> 57 |

| 7.8.16 | Floating Point XOP Package           | 7 <del>-</del> 58 |

| 7.8.17 | Variable Storage                     | 7-59              |

| 7.8.18 | ASCII Character Set                  | 7-60              |

| 7.8.19 | Hex-Decimal Table                    | 7-61              |

| 7.8.20 | Error Codes                          | 7-62              |

| 7.9    | BIBLIOGRAPHY • • • • • • • • • • •   | 7-63              |

## CHAPTER 8 ASSEMBLY LANGUAGE

| 8.1     | INTRODUCTION • • • • • • • • • • •                           | 8-1  |

|---------|--------------------------------------------------------------|------|

| 8.2     | INSTRUCTION FORMAT                                           | 8-3  |

| 8.3     | INSTRUCTION FORMAT RESTRICTIONS • • • • •                    | 8-4  |

| 8.4     | MEMORY ORGANIZATION • • • • • • • •                          | 8-5  |

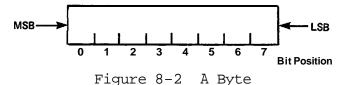

| 8.4.1   | Byte                                                         | 8-5  |

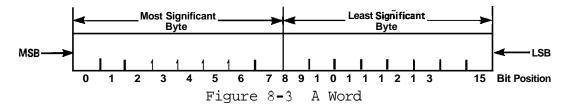

| 8.4.2   | Word                                                         | 8-5  |

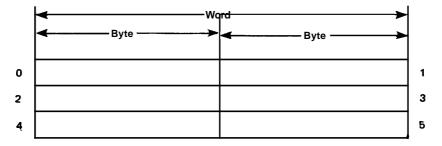

| 8.4.3   | Registers · · · · · · · · · · ·                              | 8-6  |

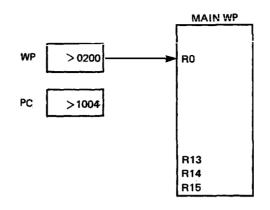

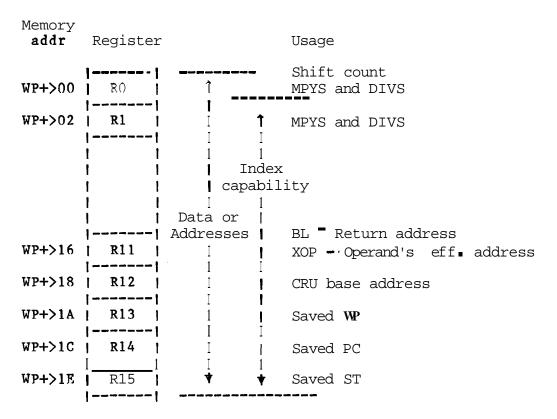

| 8.4.4   | Workspace Registers                                          | 8-7  |

| 8.4.5   | Register Functions , , , , , , , , ,                         | 8-8  |

| 8.4.6   | Context Switch                                               | 8-8  |

| 8.4.7   | Addressing Modes                                             | 8-10 |

| 8.4.7.1 | Register Addressing 🛛 🖌 🖛 🖛 🖛 🖛                              | 8-11 |

| 8.4.7.2 | Register Indirect Addressing 🕠 👝 👝 🦂                         | 8-11 |

| 8.4.7.3 | Symbolic Memory Addressing                                   | 8-12 |

| 8.4.7.4 | Indexed Memory Addressing                                    | 8-13 |

| 8.4.7.5 | Register Indirect Autoincrement Addressing                   | 8-13 |

| 8.4.8   | Specialized Addressing Modes , , , , , ,                     | 8-13 |

| 8.4.8.1 | Immediate Addressing , , , , , , , , ,                       | 8-13 |

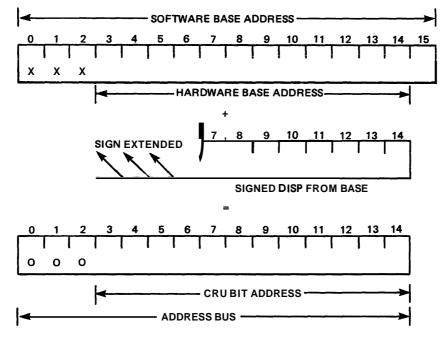

| 8.4.8.2 | CRU Bit Addressing , , , , , , , ,                           | 8-14 |

| 8.4.8.3 | Program Counter Relative Addressing                          | 8-14 |

| 8.5     | SUBROUTINES • • • • • • • • • •                              | 8-15 |

| 8.6     | PARAMETER PASSING                                            | 8-17 |

| 8.7     | STRUCTURING • • • • • • • • • •                              | 8-20 |

| 8.7.1   | Selection • • • • • • • • • • •                              | 8-20 |

| 8.7.1.1 |                                                              | 8-21 |

| 8.7.1.2 | Jump Instructions                                            | 8-22 |

| 8.7.2   | Iteration                                                    | 8-24 |

| 8.7.3   | Sequence , , , , , , , , , , , ,                             | 8-26 |

| 8.8     | PROGRAMMING FOR RX AND COMPONENT SOFTWARE                    | 8-28 |

| 8.9     | COMMUNICATIONS REGISTER UNIT • • • • • •                     | 8-30 |

| 8.9.1   | Single-Bit CRU Instructions                                  | 8-32 |

| 8.9.2   | Multiple-Bit CRU Instructions • • • • •                      | 8-33 |

| 8.10    | INTERRUPTS • • • • • • • • • •                               | 8-35 |

| 8.10.1  | Interrupt Structure , , , , , , , , ,                        | 8-36 |

| 8.10.2  | Interrupt Vectors                                            | 8-37 |

| 8.10.3  | Interrupt Sequence , , , , , , , , , ,                       | 8-38 |

| 8.10.4  | Fault Tolerant Interrupt Systems 🛛 , 🔥 ,                     | 8-40 |

| 8.11    | EXTENDED OPERATION INSTRUCTIONS , , , , ,                    | 8-41 |

| 8.11.1  | Defining Extended Operation Instructions $\bullet$ $\bullet$ | 8-42 |

| 8.11.2  | Extended Operation Instruction Vectors $\$ .                 | 8-43 |

| 8.11.3  | Extended Operation Instruction Execution $\bullet$ $\bullet$ | 8-43 |

| 8.12 9    | 900/99000 F          | Y,TTMA' | •    |         | •    |     | •     |     | • | • | 8-46              |

|-----------|----------------------|---------|------|---------|------|-----|-------|-----|---|---|-------------------|

| 8.12.1    | TMS9900              |         |      |         |      | • • |       |     |   |   | 8-46              |

| 8.12.2    | SBP9900A             |         |      |         |      |     | •     |     | • |   | 8-46              |

| 8.12.3    | TMS9980A             | -       |      |         | -    |     | -     |     | - | - | 8-47              |

| 8.12.4    | TMS9981 .            |         | • •  |         | -    |     |       |     |   | - | 8-47              |

| 8.12.5    | TMS9995              |         |      | •       |      |     | -     |     |   | - | 8-47              |

| 8.12.1    | Macro In             |         |      |         |      |     |       |     |   | • | 8-47              |

| 8.12.2    | Arithmet             |         |      |         |      |     | •     |     | • | • | 8-48              |

| 8.12.3    | Test for             |         |      |         |      |     |       |     | • | • | 8-48              |

| 8.12.4    | On Chip              |         |      |         |      |     |       | • • |   | • | 8-48              |

|           | -                    |         | -    | -       |      |     |       |     | • | • | 8-49              |

| 8.12.5    | On Chip<br>SBP9989 . |         |      |         |      |     |       |     | • | • |                   |

| 8.12.6    |                      |         |      |         |      |     |       | • • |   |   | 8-50              |

| 8.12.6.1  | MPILCK .             |         |      | •       |      |     |       | ••• |   |   | 8-50              |

| 8.12.6.2  |                      | •       |      |         |      |     |       |     |   |   | 8-51              |

| 8.12.6.3  |                      | •       |      |         |      |     |       |     |   |   | 8-51              |

| 8.12.7    | <b>TMS99000</b> F    |         |      |         |      |     |       |     |   |   | 8-51              |

| 8.12.7.1  | Macrosto             |         |      |         |      |     |       | • • |   |   | 8-52              |

| 8.12.7.2  | Attached             |         |      |         |      |     |       |     |   |   | 8 <del>-</del> 53 |

| 8.12.7.3  | Attached             |         |      |         |      |     |       |     |   |   | 8-55              |

| 8.12.7.4  | Interrup             |         |      |         |      |     |       |     |   |   | 8-55              |

| 8.12.7.5  |                      |         |      |         |      |     |       |     |   |   | 8-56              |

| 8.12.7.6  | CRU Oper             | ation   | .s • | •       | •    | • • | •     | • • | • | • | 8-56              |

| 8.13 A    | LGORITHMS A          |         |      |         |      |     |       |     |   | • | 8-58              |

| 8.13.1    | Invoking t           | he 99   | 00 F | 'amily  | y of | Ass | emble | ers |   | • | 8-58              |

| 8.13.1.1  | LBLA •               | •       | • •  | •       | •    | • • | •     |     | • | • | 8-58              |

| 8.13.1.2  | SYMBOLIC             | •       |      | •       | •    | • • | •     | • • | • | • | 8-59              |

| 8.13.1.3  |                      | •       |      |         |      |     |       |     |   |   | 8-60              |

| 8.13.1.4  |                      | •       |      |         |      |     |       |     |   |   | 8-61              |

| 8.13.2    | Number Rep           | resen   | tati | ons     | •    |     | •     |     | • | • | 8-62              |

| 8.13.2.1  | Number S             |         |      |         |      |     |       |     |   |   | 8-63              |

| 8.13.2.2  | Represen             |         |      |         |      |     |       |     |   |   | 8-64              |

| 8.13.2.3  | Represen             |         |      |         |      |     |       |     |   |   | 8-65              |

| 8.13.2.4  | Represei             |         |      |         |      |     |       |     |   |   | 8-66              |

| 8.13.2.5  | Binary C             |         |      |         |      | -   | -     |     | - |   | 8-67              |

| 8.13.3    | Position I           |         |      |         |      |     |       |     |   |   | 8-67              |

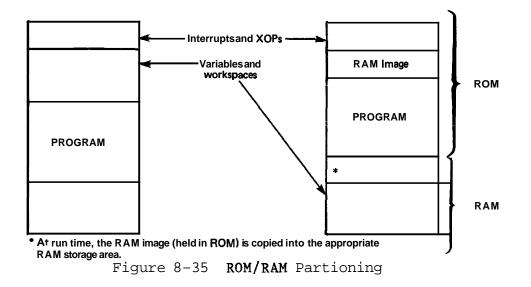

| 8.13.4    | ROM/RAM Sy           |         |      |         |      |     |       |     |   |   | 8-69              |

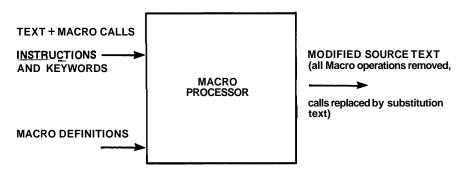

| 8.13.5    | Macro Proc           |         |      |         |      |     |       | • • |   | • | 8-71              |

| 8.13.5.1  | Macro De             |         | •    | •       | •    |     | •     |     |   |   | 8-73              |

| 8.13.5.2  | Macro Ca             |         |      | _       | -    |     |       |     |   | - | 8-73              |

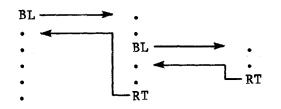

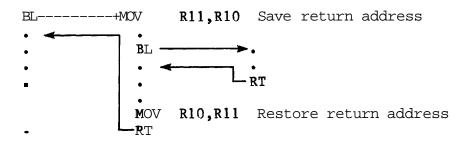

| 8.13.6    | Nested Sub           |         |      |         | -    |     |       |     |   | - | 8-75              |

| 8.13.7    |                      | •       |      |         |      |     |       | • • | • | - | 8-76              |

| 8.13.8    | Recursion            | •       | • •  | •       |      |     |       | ••• | • | • | 8-77              |

| 8.13.9    | Re-entranc           |         | •••  |         |      | ••• |       | ••• | • |   | 8-78              |

| 8.13.10   | Automatic            | 4       |      |         |      |     |       |     | • | • | 8-78              |

| 8.13.11   |                      |         | -    | • AII(  |      |     |       |     | • |   | 8-82              |

| 8.13.12   | Jump Table           |         |      |         |      |     |       |     |   | • | 8-84              |

|           | Miscellane           | eous T  | ecin | IIques  | 3    | • • | •     | • • | • | • |                   |

| 8.13.12.1 | Swapping             |         |      |         |      |     | ٠     |     | • | ٠ | 8-84<br>8-85      |

| 8.13.12.2 | Error Re             |         |      |         |      |     | ٠     |     |   | • | 8-85              |

| 8.13.12.3 | Buffered             |         |      | •<br>br |      |     | •     |     | • | ٠ |                   |

| 8.13.12.4 | Incremen             |         |      |         |      |     |       |     | • | • | 8-88              |

| 8.13.12.5 | Non Dest             |         |      |         |      |     |       | • • | • | • | 8-88              |

| 8.13.12.6 | Simple C             |         |      |         |      |     |       | • • | ٠ | • | 8-88              |

| 8.13.12.7 | Simple 1             |         |      |         |      |     |       |     | • | • | 8-91              |

| 8.13.12.8 | Automati             |         |      |         |      |     |       |     |   | • | 8-93              |

| 8.13.12.9 | Packed D             | ata     | • •  | +       | ٠    | , , | •     | • • | ٠ | • | 8-95              |

| 8.14      | REFERENCE SECTION • • • • • • • • •   | 8-96               |

|-----------|---------------------------------------|--------------------|

| 8.14.1    | Instruction Formats                   | 8-96               |

| 8.14.2    | Status Register 🕠 🗛 🦂 🦂 🦂 🔹 🗛 👘       | 8-97               |

| 8.14.3    | Interrupts                            | 8-98               |

| 8.14.4    | CRU • • • • • • • • • • • • •         | 8-99               |

| 8.14.5    | Register Restrictions • • • • • • • • | 8-99               |

| 8.14.6    | Assembly Language Instructions        | 8-100              |

| 8.14.7    | Pseudo-Instructions                   | 8-103              |

| 8.14.8    | Assembler Directives • • • • • • • •  | 8-104              |

| 8.14.9    | Object Record Format and Code 🛛 🔹 🔹 🔹 | 8-107              |

| 8.14.10   |                                       | 8-108              |

| 8.14.10   | .1 TMS9900                            | 8-108              |

| 8.14.10.2 |                                       | 8-110              |

| 8.14.10   |                                       | 8-111              |

| 8.14.10   |                                       | 8-113              |

| 8.14.10.5 |                                       | 8-115              |

| 8.14.10.6 | 5 TMS99000 Family                     | 8-118              |

| 8.14.11   | Pin Assignments • • • • • • • • • •   | 8-121              |

| 8.14.11.1 |                                       | 8-121              |

| 8.14.11.2 | 2 TMS9980A                            | 8-121              |

| 8.14.11.3 |                                       | 8-122              |

| 8.14.11.4 |                                       | 8-122              |

| 8.14.11   |                                       | 8-123              |

| 8.14.11.6 |                                       | 8-123              |

| 8.14.11.7 | 7 TMS99000 Family                     | 8-124              |

| 8.14.12   | ASCII Character Set 🔹 🔹 🔹 🔹 🔹 🔹 🔹     | 8 <del>-</del> 125 |

| 8.14.13   | Hex-Decimal Table                     | 8-126              |

| 8.15      | BIBLIOGRAPHY                          | 8-127              |

#### LIST OF TABLES

| Table | Title                                      | Page |

|-------|--------------------------------------------|------|

| 1-1   | Semiconductor Memory Characteristics , , , | 1-19 |

| 4-1   | Methods of Parameter Passing               | 4-44 |

| 8-1   | Interrupt Mask Table                       | 8-37 |

| 8-2   | Interrupt Vector Table                     | 8-38 |

| 8-3   | XOP Vector Table                           | 8-44 |

#### LIST OF FIGURES

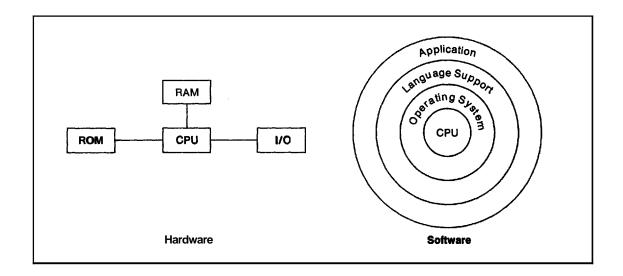

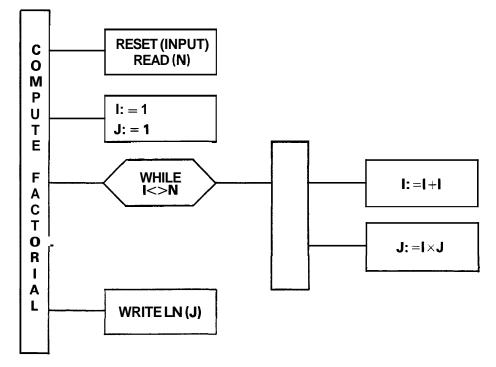

#### Figure Title Page 1-1 Conventional Machine • • 1-1 . . . 1-1 1-2 Microprocessor Machine . . . . . . . . 1-2 1-3 Layout of a Microprocessor Machine . . . 1-3 1-4 Program Control . . . . 1-5 1-4 Software Has No Unique Physical Form • • • 1-5 1-6 "Black Box" 🔹 🔹 🔹 -. • . . . 1-6 1-7 AND Gate . . . . . • • • -1-8 AND Gate Truth Table 🔹 🔹 . . . 1-6 . . .

| -              |                                                  |      |

|----------------|--------------------------------------------------|------|

| 1-9            | Data Translation                                 | 1-7  |

| 1-10           | Computer                                         | 1-10 |

| 1-11           | Structure of a Computer , , , , , , , , ,        | 1-11 |

| 1-12           | A General Purpose Computer                       | 1-14 |

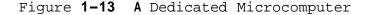

| 1-13           | A Dedicated Microcomputer                        | 1-16 |

| 1-14           | Electronic Function Package                      | 1-22 |

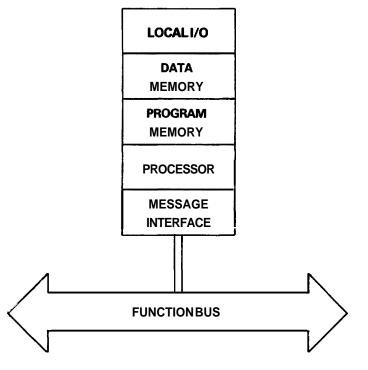

| 2-1            | 5                                                | 2-2  |

| 2-1<br>2-2     | The Software Development Process , , , , ,       |      |

|                | Hardware Design for a Microprocessor System      | 2-8  |

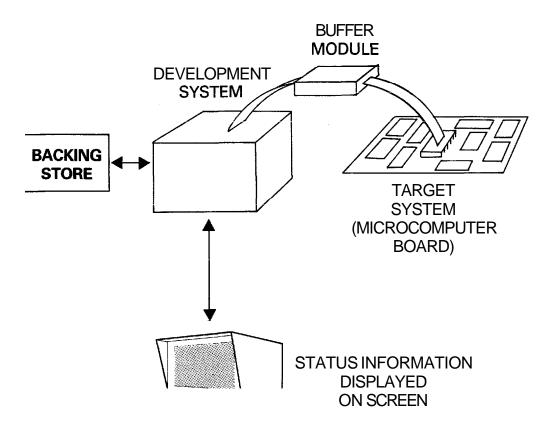

| 2-3            | Emulation • • • • • • • • • • •                  | 2-17 |

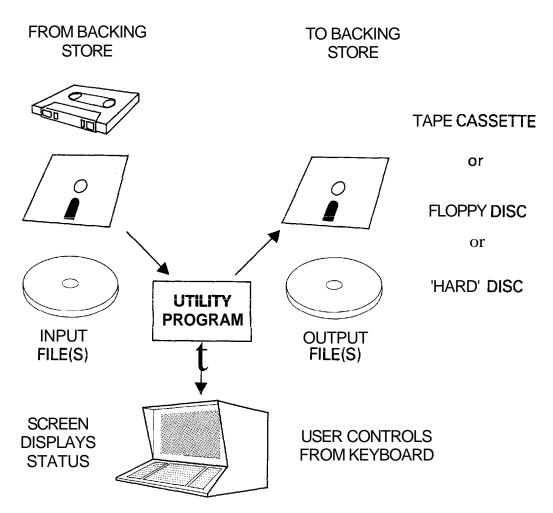

| 3-1            | Software Tools                                   | 3-3  |

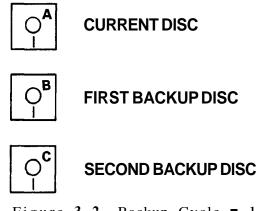

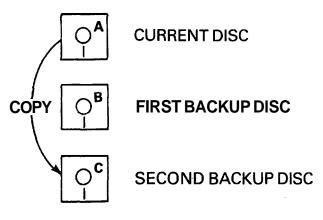

| 3-2            | Backup Cycle _ 1 , , , , , , , , , , ,           | 3-4  |

| 3-3            | Backup Cycle _ 2 • • • • • • • • • •             | 3-4  |

| 3-4            | Backup Cycle _ 3 , , , , , , , , , ,             | 3-5  |

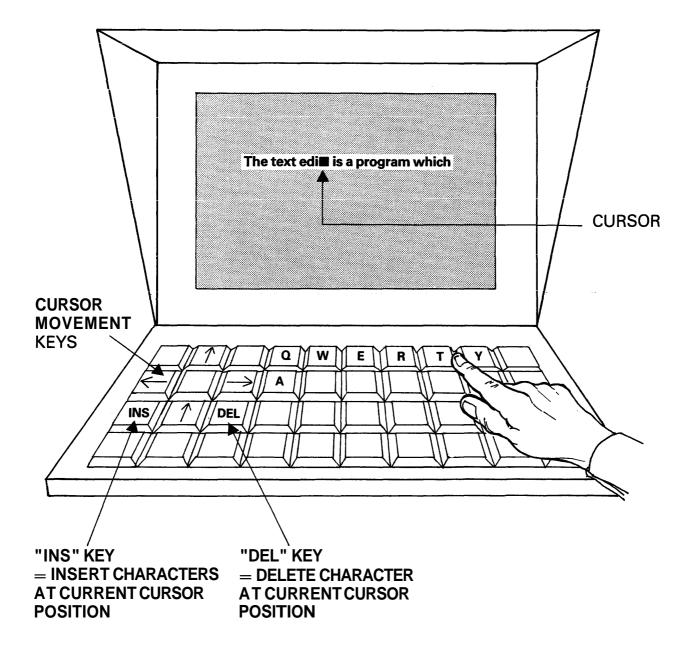

| 3-5            | Editor Function                                  | 3-6  |

| 3-6            | Use of a Screen Based Editor                     | 3-7  |

| 3-7            | Microprocessor Pascal Editor 'Menu' of Commands  | 3-8  |

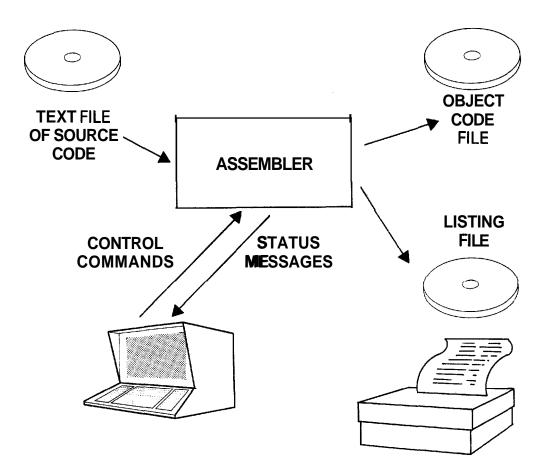

| 3-8            | -                                                | 3-10 |

|                |                                                  |      |

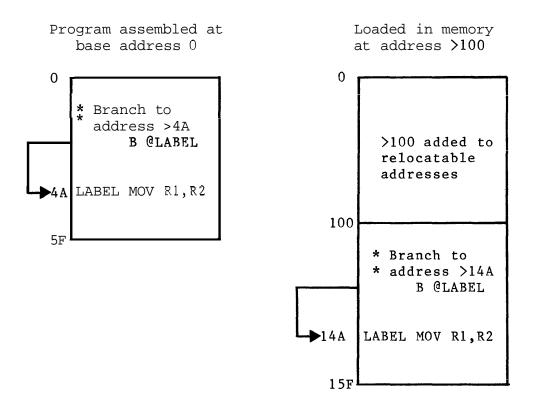

| 3-9            | Relocatable Code                                 | 3-17 |

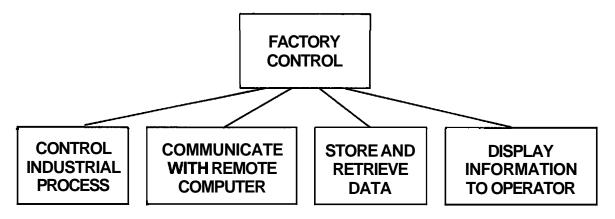

| 4-1            | Component Packages of a Factory Control System   | 4-3  |

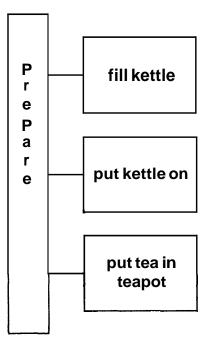

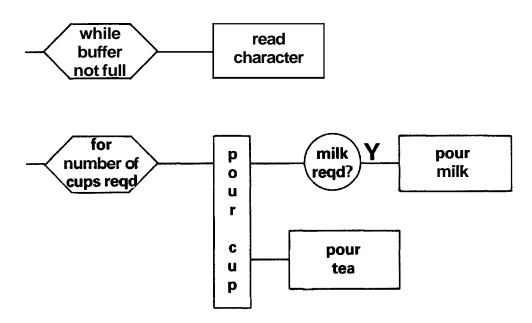

| 4-2            | Tea making Algorithm , , , , , , , , , ,         | 4-6  |

| 4-3            | "Pour cup" Algorithm                             | 4-6  |

| 4-4            | Sequence Structure Diagram                       | 4-8  |

| 4-5            | Selection Structure Diagram                      | 4-9  |

| 4-6            | "Pour cup" Structure Diagram , , , , , ,         | 4-10 |

| 4-7            | Alternative Algorithm for "pour cup"             | 4-11 |

| 4-8            | The CASE Construct                               | 4-14 |

| 4-9            |                                                  | 4-14 |

| 4-10           |                                                  |      |

|                | Iteration Structure Diagram                      | 4-16 |

| 4-11           | Data Representation of a Temperature , , ,       | 4-20 |

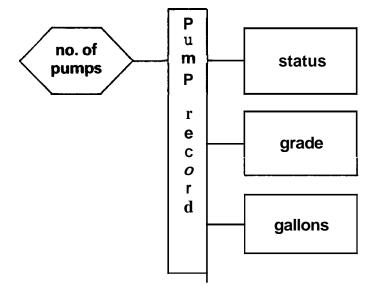

| 4-12           | Data Diagram for an Array of Records             | 4-32 |

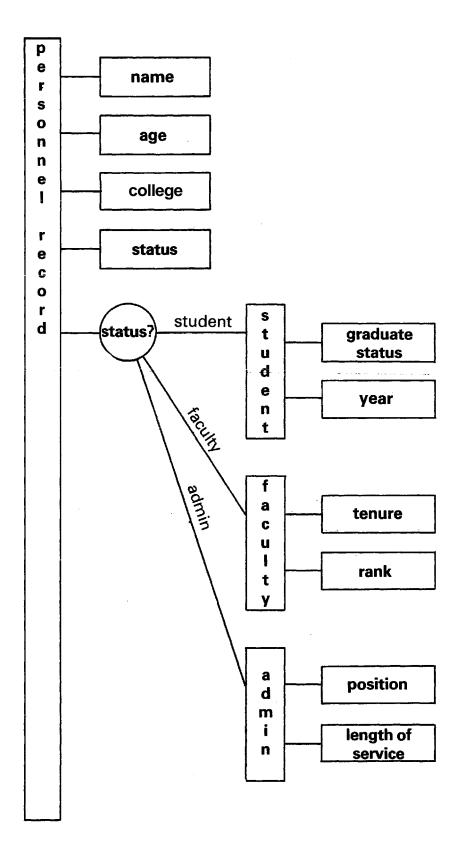

| 4-13           | The Record Variant                               | 4-33 |

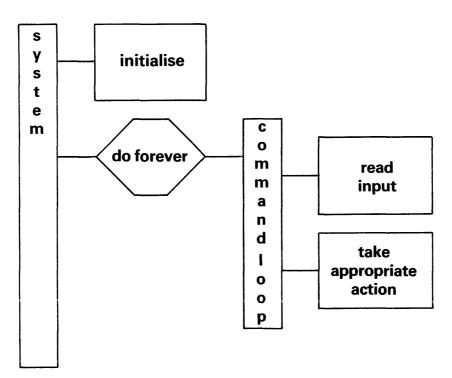

| 4-14           | Initial Design Algorithm 🕠 🦂 🦂 🦂 .               | 4-36 |

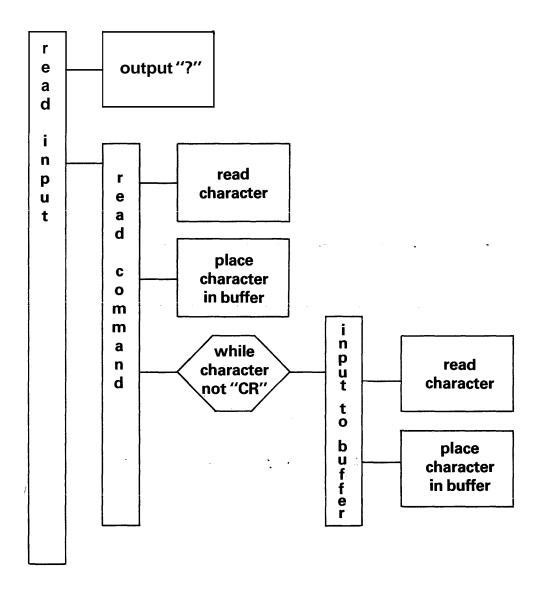

| 4-15           | "Read Input" Algorithm Expansion , 🕠 , ,         | 4-37 |

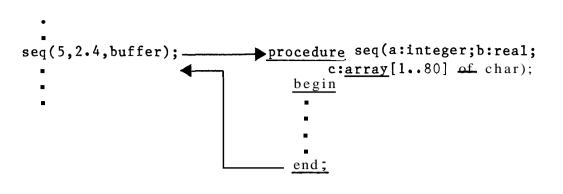

| 4 <b>-</b> 16a | Procedure Declaration                            | 4-40 |

| 4 <b>-</b> 16b | Procedure Call , , , , , , , , , , ,             | 4-41 |

| 4-17           | Function Declaration and Reference , , , ,       | 4-41 |

| 4-18           | Procedure Call Mechanism                         | 4-42 |

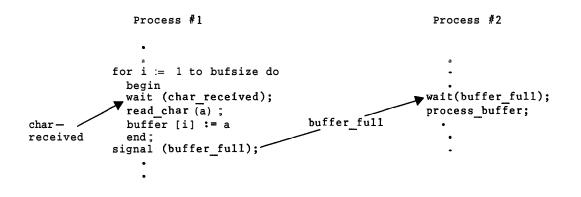

| 4-19           | Semaphore Signalling                             | 4-46 |

| 4-20           |                                                  | 4-49 |

|                |                                                  |      |

| 4-21           | Compilation Listing for the Tea Making Algorithm | 4-50 |

| 4-22           | Corrected Compilation Listing                    | 4-51 |

| 4-23           | Reverse Assembled Object Code for the Tea Making |      |

|                | Algorithm                                        | 4-53 |

| 5-1            | Configuration of Component Software Packages .   | 5-2  |

| 5-2            | The Traditional Approach , , , , , , ,           | 5-4  |

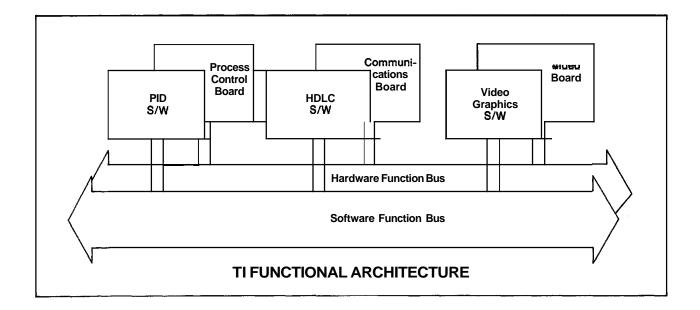

| 5-3            | TI Functional Architecture                       | 5-5  |

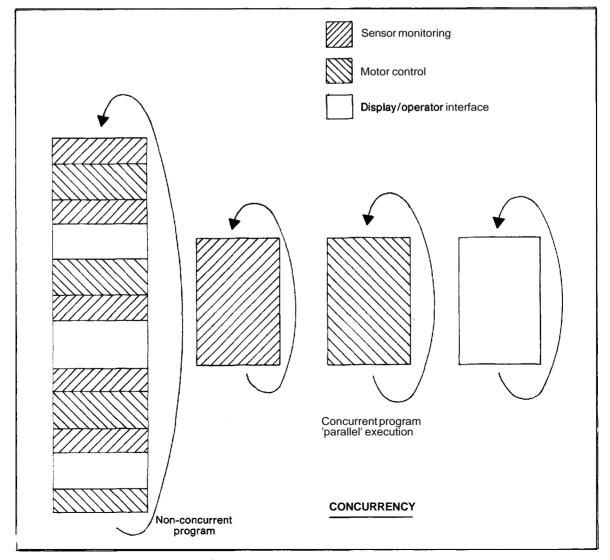

| 5-4            | Concurrency                                      | 5-7  |

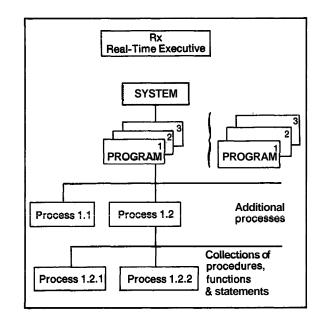

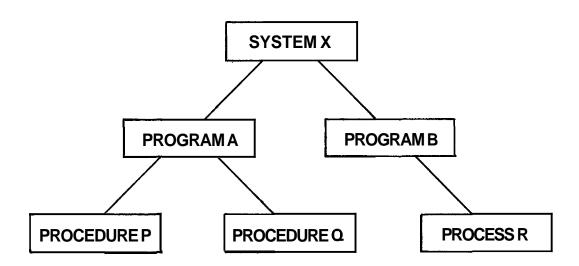

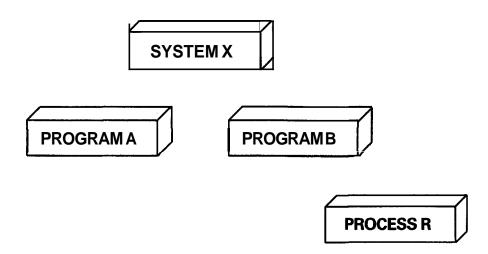

| 5-5            | SYSTEMS, PROGRAMs and PROCESSes                  | 5-13 |

| 5-6            | -                                                | 5-18 |

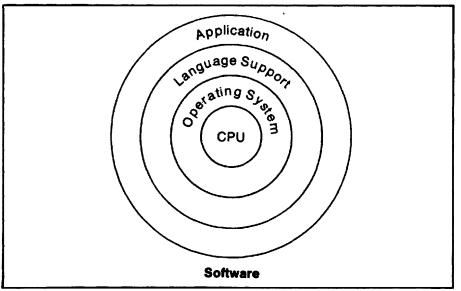

| 5-7            | Conventional Operating System Structures • •     | 5-18 |

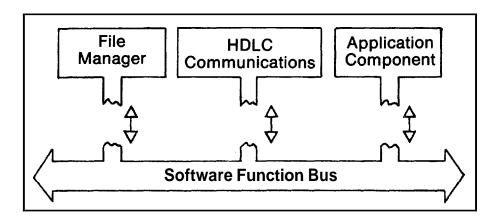

|                | Software Function Bus                            |      |

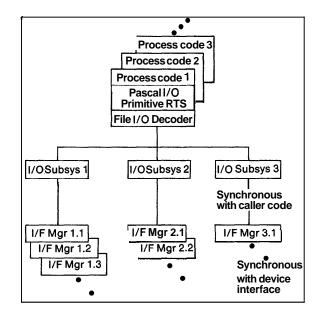

| 5-8            | I/O Subsystem                                    | 5-20 |

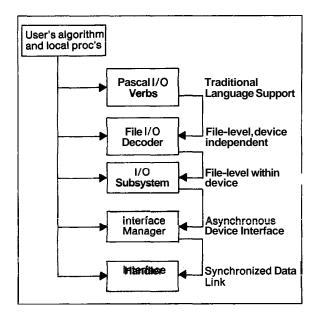

| 5-9            | 5 Levels of Interface to I/O Subsystems          | 5-21 |

| 5-10           | Configuration                                    | 5-22 |

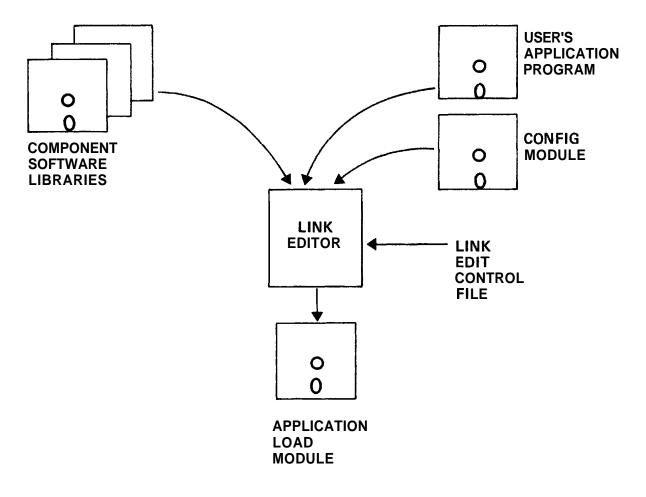

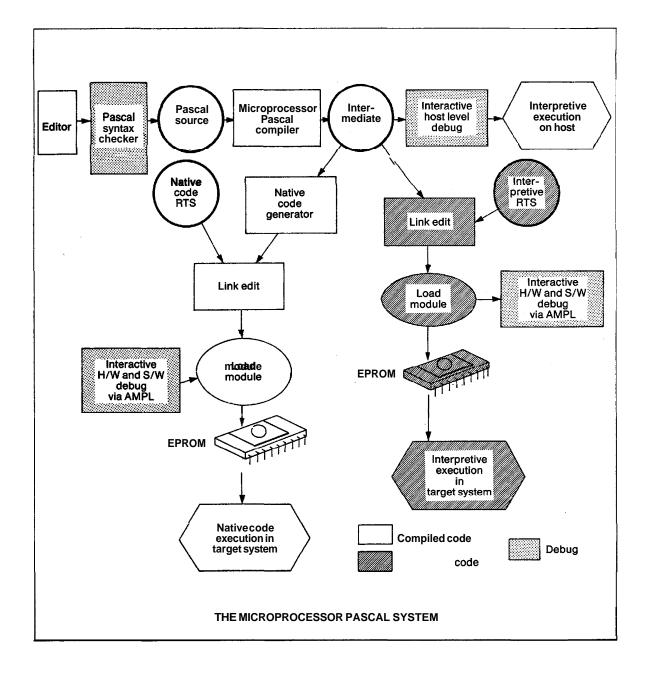

| 5-11           | The Microprocessor Pascal System                 | 5-25 |

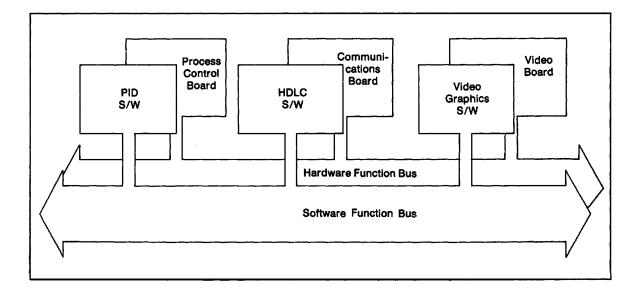

| 5-12           | Software/Hardware Correspondence                 | 5-27 |

|                | -                                                |      |

х

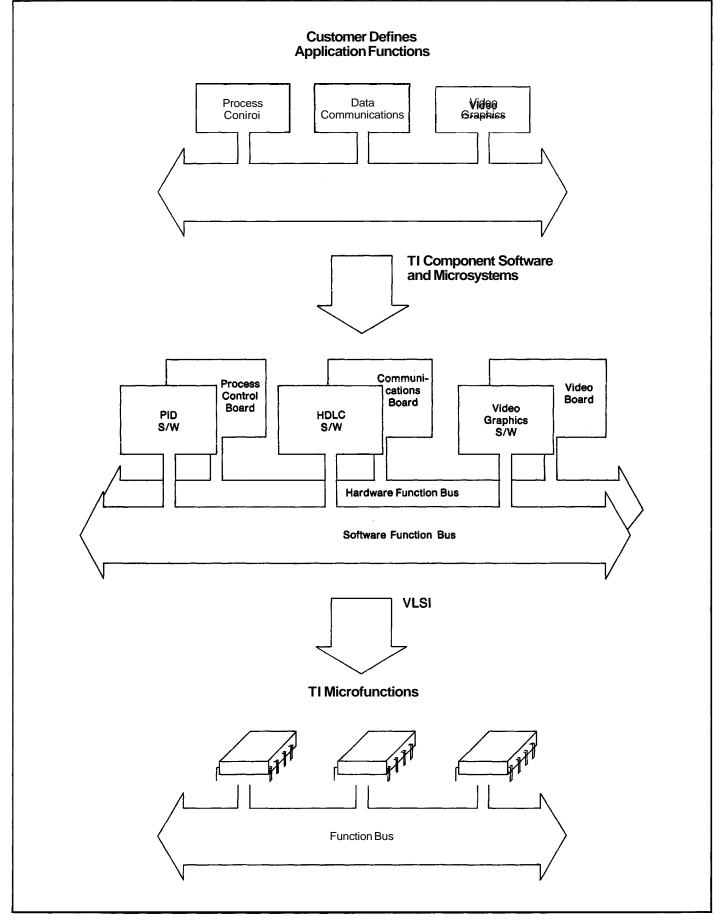

| 5-13         | The Functional Approach • • • • • • • •              | 5-29              |

|--------------|------------------------------------------------------|-------------------|

| 6-1          | Program Structure Diagram • • • • • • •              | 6-7               |

| 6-2          | System Structure • • • • • • • • • •                 | 6-9               |

| 6-3          | Lexical Hierarchy                                    | 6-10              |

| 6-4          | Concurrent Hierarchy                                 | 6-10              |

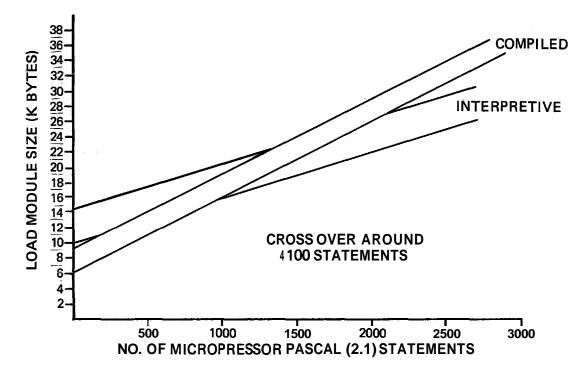

| 6-5          | Interpretive vs Compiled Characteristcis 🔒 🔒         | 6-15              |

| 6-6          | Repeat Until Construct , , , , , , , ,               | 6-43              |

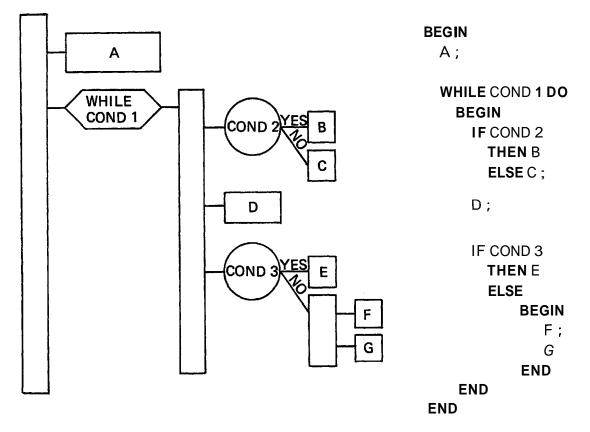

| 6-7          | A Sample Program                                     | 6-43              |

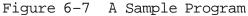

| 6-8          | Channel Mechanism                                    | 6-53              |

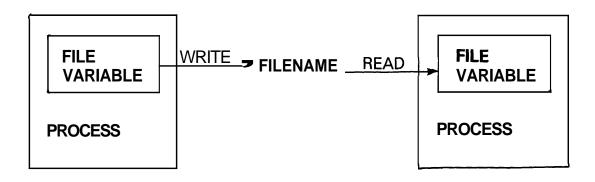

| 6-9          | Interprocess File Mechanism                          | 6-56              |

| 6-10         | DVM Example _ Lexical Hierarchy , , , , ,            | 6-65              |

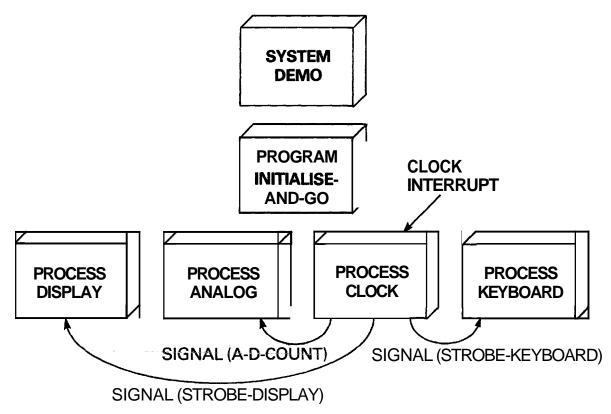

| 6-11         | DVM Example - Concurrent Structure                   | 6-65              |

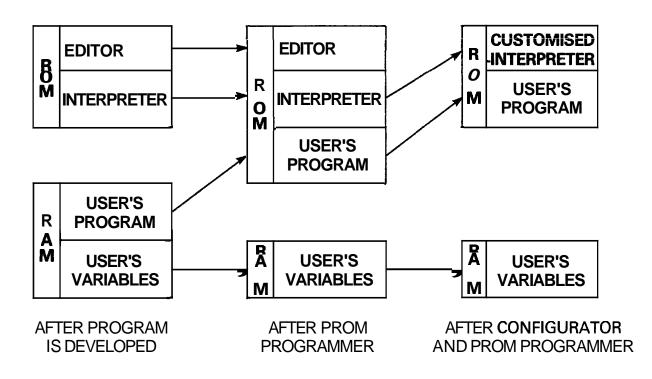

| 7-1          | Code Minimisation                                    | 7-8               |

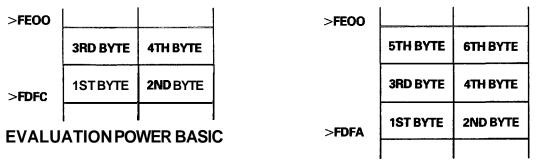

| 7-2          | First Variable Allocation                            | 7-36              |

| 7-3          | Second Variable Allocation                           | 7-36              |

| 7 <b>-</b> 4 | Integer Format                                       | 7-36              |

| 7 <b>-</b> 5 | Floating Point Format                                | 7-37              |

| 7-6          | Character String Format                              | 7-38              |

| 7-7          | Character String Storage Example                     | 7-38              |

| 7-8          | Array Storage                                        | 7-39              |

| 7-9          | System Memory Map                                    | 7-41              |

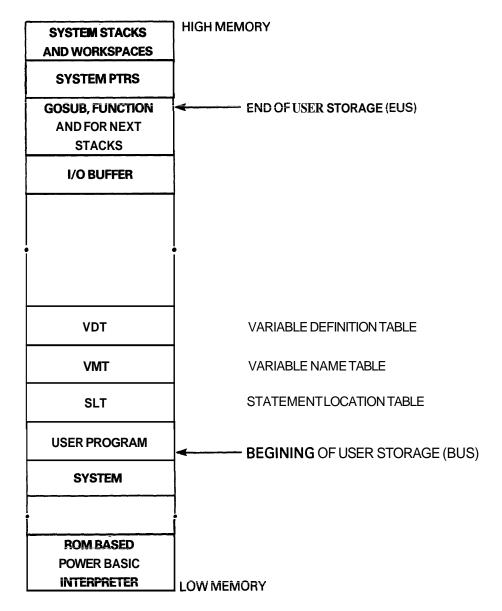

| 8-1          | Assembly Language and the Computer                   | 8-1               |

| 8-2          |                                                      | 8-1<br>8-5        |

| 8-3          | A Byte                                               | 8-5<br>8-5        |

|              |                                                      |                   |

| 8-4          | Memory Organisation                                  | 8-6               |

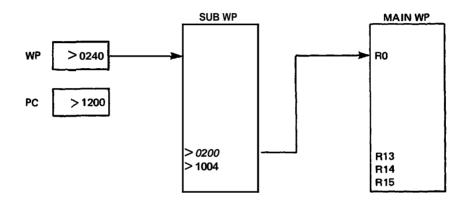

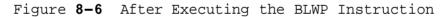

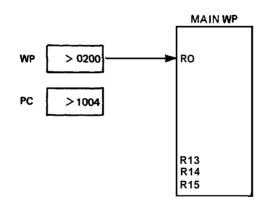

| 8-5          | Before Executing the BLWP Instruction                | 8-10              |

| 8-6          | After Executing the BLWP Instruction                 | 8-10              |

| 8-7          | After Executing the RTWP Instruction                 | 8 <del>-</del> 10 |

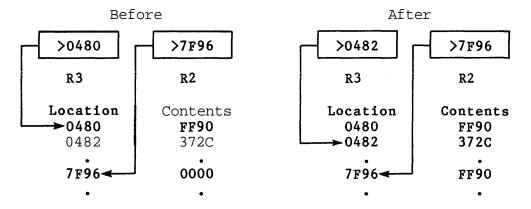

| 8-8          | Parameter Passing 1                                  | 8-18              |

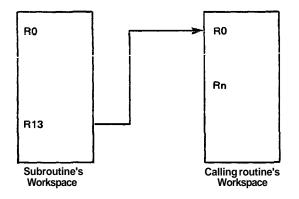

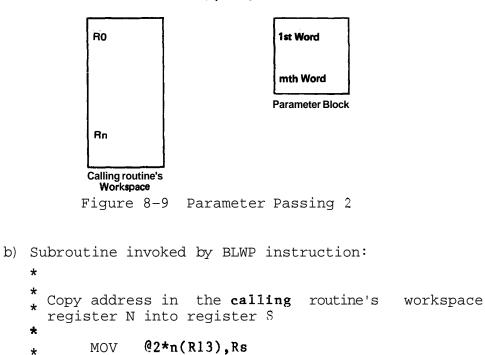

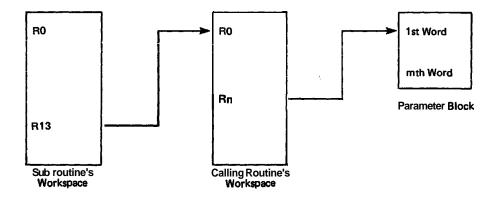

| 8-9          | Parameter Passing 2                                  | 8-18              |

| 8-10         | Parameter Passing 3                                  | 8-19              |

| 8-11         | General Selection Construct                          | 8-21              |

| 8-12         | Condition Codes for the TMS9900 Status Register      | 8-21              |

| 8-13         | A Three Way Selection Example                        | 8-22              |

| 8-14         | A Two Way Selection Example                          | 8-23              |

| 8-15         | An Iteration Example (REPEAT) , , , , , ,            | 8-24              |

| 8-16         | An Iteration Example(WHILE)                          | 8-25              |

| 8-17         | A Sequence Example                                   | 8 <del>→</del> 26 |

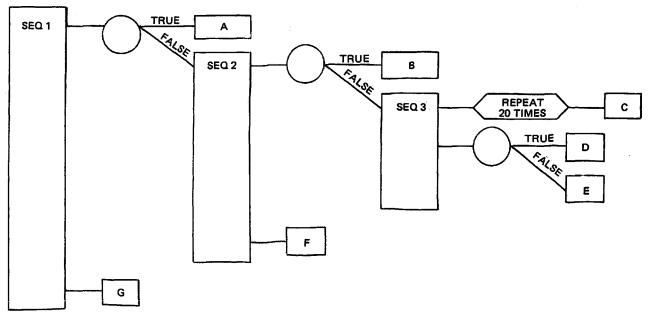

| 8-18         | A Complex Structure                                  | 8 <del>-</del> 27 |

| 8-19         | CRU Bit Addressing                                   | 8-32              |

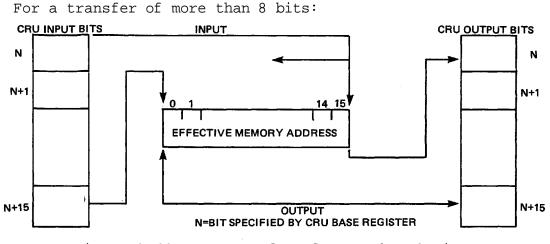

| 8-20         | CRU Transfer of More Than 8 Bits • • • • •           | 8-34              |

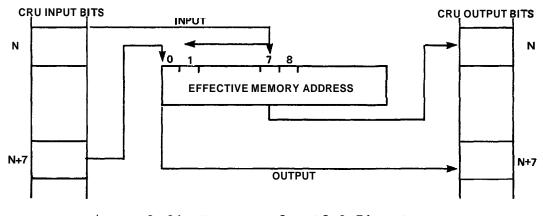

| 8-21         | CRU Transfer of $8$ Bits Or Less $\cdot$ , $\cdot$ , | 8-34              |

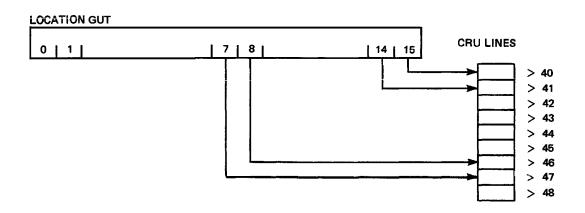

| 8-22         | CRU Output Example                                   | 8-35              |

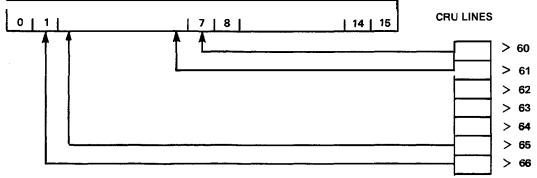

| 8-23         | CRU Input Example • • • • • • • • • • •              | 8 <del>-</del> 35 |

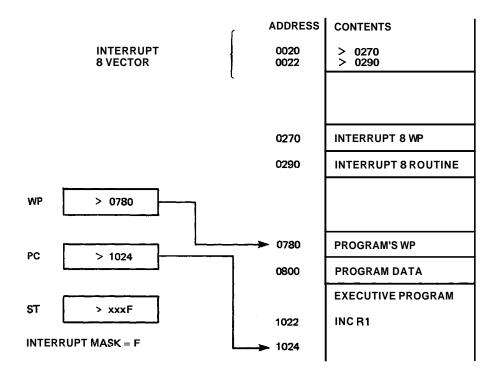

| 8-24         | State Prior to a Level 8 Interrupt • • • •           | 8-39              |

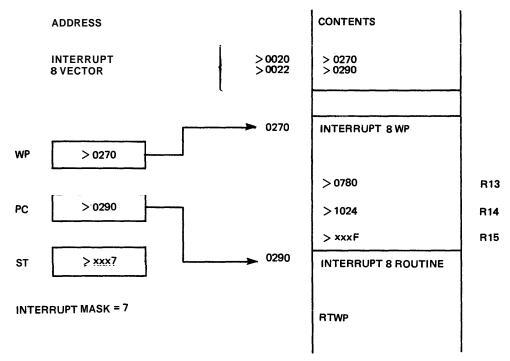

| 8-25         | State After a Level 8 Interrupt                      | 8-40              |

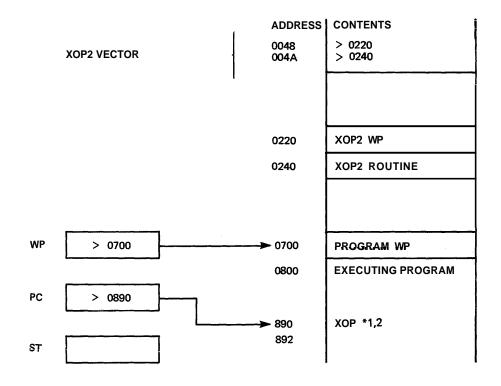

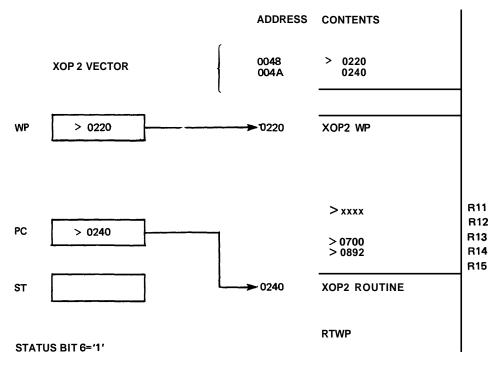

| 8-26         | State Before Executing the XOP 2 Instruction .       | 8-45              |

| 8-27         | State After Executing the XOP 2 Instruction          | 8-45              |

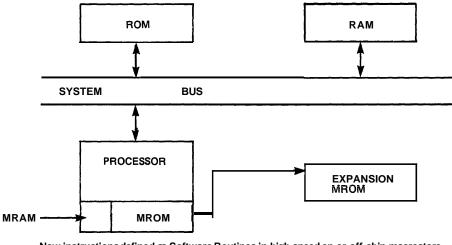

| 8-28         | Macrostore                                           | 8-53              |

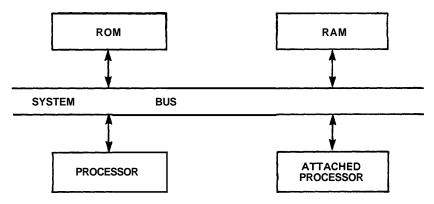

| 8-29         | Attached Processor                                   | 8-54              |

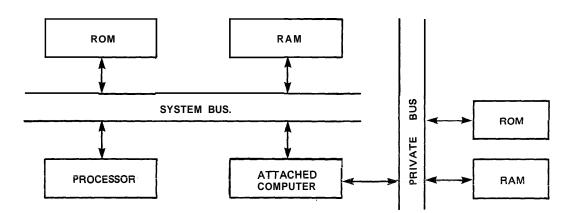

| 8-30         | Attached Computer                                    | 8-55              |

| 8-31         | Full TMS99000 Instruction Sequence                   | 8-56              |

| 8-32         | Bit Grouping                                         | 8-64              |

| 8-33         | Floating Point Format                                | 8-66              |

| 8-34         | A Possible BCD Format                                | 8-67              |

|              |                                                      |                   |

\*

| 8-35 | ROM/RAM Partitioning                        | 8-69 |

|------|---------------------------------------------|------|

| 8-36 | Macro Processor Operation                   | 8-72 |

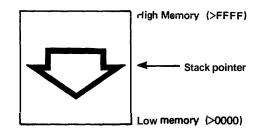

| 8-37 | Stack Representaion • • • • • • • • •       | 8-76 |

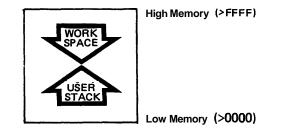

| 8-38 | A Stack/Workspace Allocation Implementation | 8-80 |

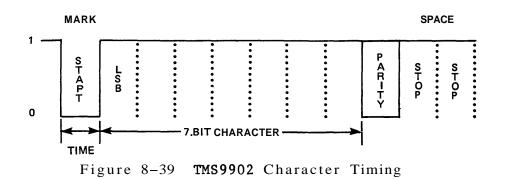

| 8-39 | TMS9902 Character Timing                    | 8-93 |

## CHAPTER 1

## INTRODUCTION

## 1.1 WHAT IS SOFTWARE?

Software is what makes microprocessor technology different from conventional engineering techniques. Fundamentally, software is a set of instructions that tells the hardware (the microprocessor, and any electrical or mechanical devices connected to it) what to do.

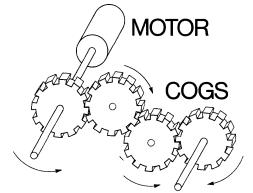

In a conventional machine, the physical layout of the parts determines what the machine will do:

Figure 1-1 Conventional Machine

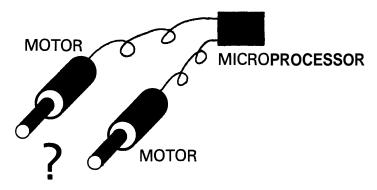

In a microprocessor machine, it is not always possible to tell from the physical arrangement exactly what the machine does:

Figure 1-2 Microprocessor Machine

The function of the machine is determined by software.

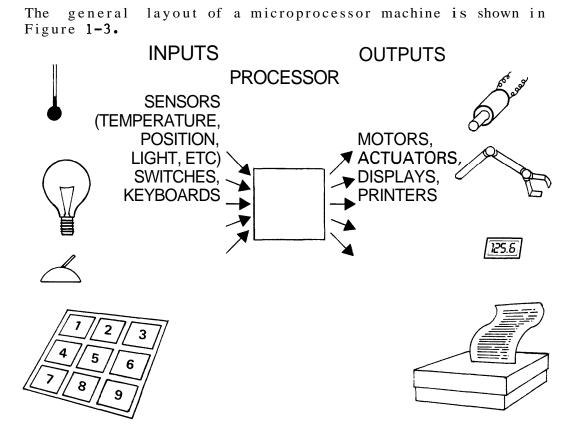

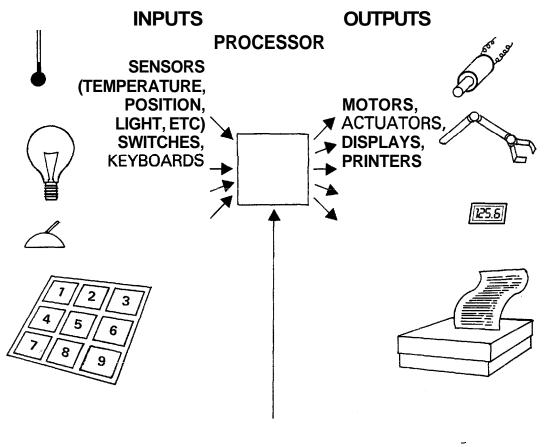

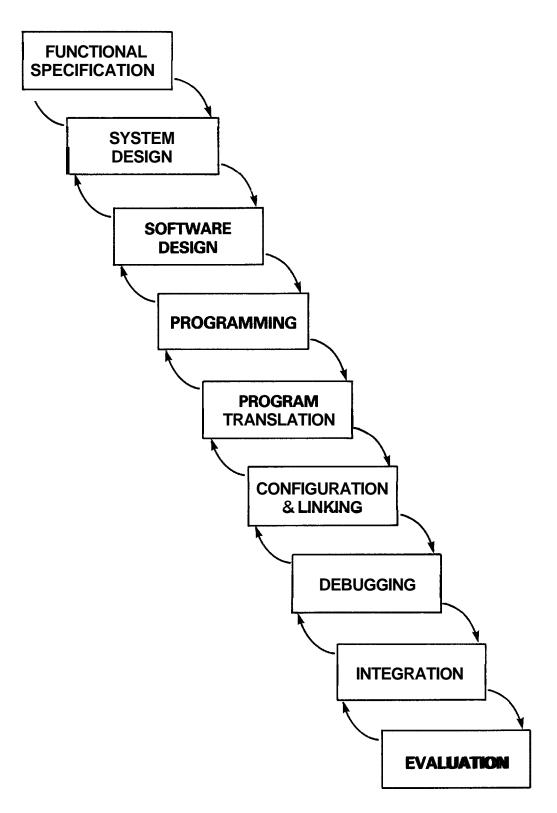

Figure 1-3 Layout of a Microprocessor Machine

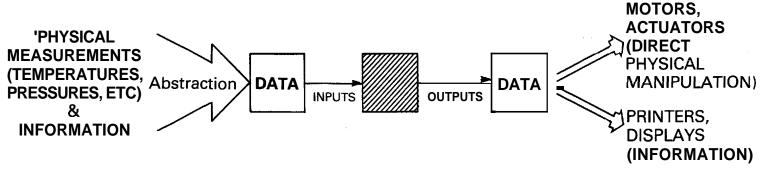

In the centre is the microprocessor. To the processor are brought a series of inputs - which might come from temperature sensors, limit switches, operator keyboards and so on, All inputs must be converted to electrical signals before they reach the processor.

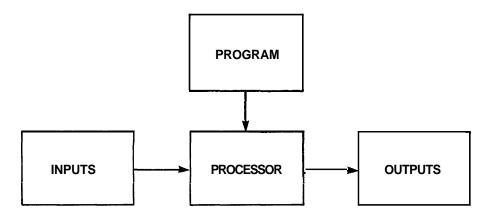

From the processor come a collection of outputs - again electrical signals, which can be used to operate motors, actuators, displays and so on, The processor itself has an extensive repertoire of operations it can perform, involving inputs, outputs and internal manipulations. However, by itself the processor is useless, It needs a program - a set of software instructions that specify exactly what operations to perform, and in what order. The program will determine when to take notice of (to read) the input signals, what to do with them, and what output signals to produce. It is the program that controls the machine.

PROGRAM

Figure 1-4 Program Control

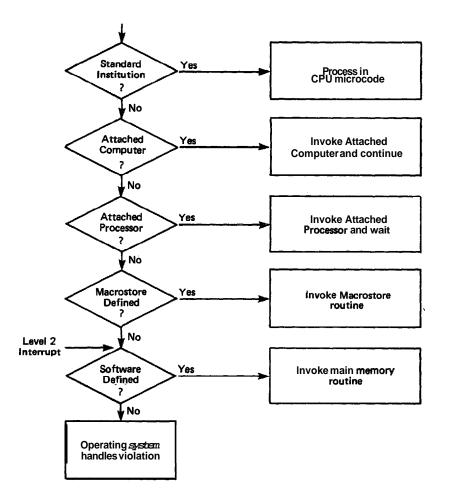

One characteristic of microprocessor systems is that a different program placed in the 'same set of hardware will cause the machine to do different things. Of course, the scope of what can be done is determined by the hardware: if there is not a motor control circuit connected to a microprocessor, there is no way that the software will be able to turn a motor on and off. It is the hardware that determines what is possible; it is the software that determines what the machine actually does.